# E<sup>2</sup>PROM CMOS PROGRAMMABLE LOGIC DEVICE

- HIGH PERFORMANCE SGS-THOMSON SINGLE-POLY E<sup>2</sup>PROM CMOS TECHNOLOGY

- 20ns maximum propagation delay (GAL16V8S-20Exx)

- F<sub>max</sub> = 41.6MHz

- 15ns max. from clock input to data output

- TTL compatible 24mA outputs

- SGS-THOMSON proprietary Single-Poly F3-G™ technology

- VERY LOW POWEŔ

- 24mA typ. (27mA max.) I<sub>CC</sub>

- ELECTRICAL ERASABLE CELL TECHNOLOGY

- Reconfigurable logic/reprogrammable cells

- 100% tested: guaranteed 100% final programming yield

- High speed electrical program & erase

- EIGHT OUTPUT MACROCELLS

- Maximum flexibility for complex logic design

- Programmable output polarity

- Also emulates 21 types of 20 pin PAL® devices with full function/fuse map/parametric compatibility

- PRELOAD AND POWER-ON RESET OF ALL REGISTERS

- 100% functional testability

- ELECTRONIC SIGNATURÉ FOR USER'S IDENTIFICATION

#### DESCRIPTION

The GAL16V8S, at 20ns maximum propagation delay time, combines a high performance CMOS process with Electrical Erasable Single-Poly F3-G™ technology — SGS-THOMSON proprietary — to provide one of the highest performance-cost2 produsct available in PLD market.

CMOS circuit allows GAL16V8S to consume just 24mA (typ.) Icc which represents a 85% saving in power when compared to its bipolar counterparts. Its E<sup>2</sup>PROM CMOS technology offers high speed (50ms) erase time providing the ability to reprogram or reconfigure the device quickly and efficiently.

GAL16V8S features 8 programmable Output Logic Macro Cells (OLMCs) allowing each output to be configured by the user. Additionally, the GAL16V8S is capable of emulating, in a functional/fuse

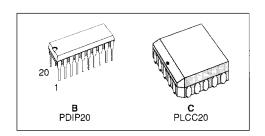

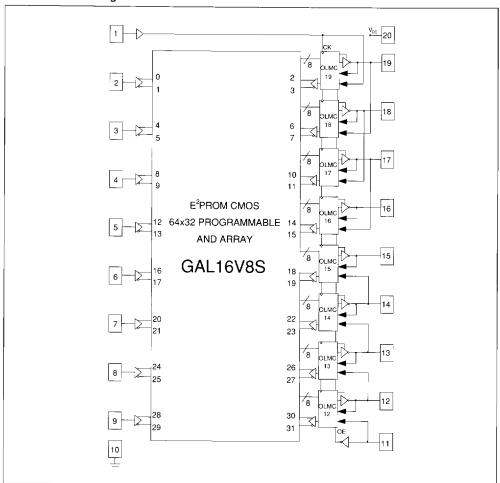

#### Pin Connections

#### Pin Names

| 111111111111111111111111111111111111111 |               |  |  |  |

|-----------------------------------------|---------------|--|--|--|

| I0–I9                                   | Input         |  |  |  |

| CLK Clock Input                         |               |  |  |  |

| F <sub>0</sub> –F <sub>7</sub>          | I/O           |  |  |  |

| ŌĒ                                      | Output Enable |  |  |  |

| Vcc                                     | Power         |  |  |  |

| GND                                     | Ground        |  |  |  |

GAL® is a registered trademark of Lattice Semiconductor Corp.; PAL® is a registered trademark of Monolithic Memories Inc.

map/parametric compatible mode, 21 types of 20 pin PAL® devices. Unique test circuits and reprogrammable cells allow complete AC, DC and functional testing during manufacture.

Therefore, SGS-THOMSON guarantees 100% field programmability and functionality of GAL® devices. SGS-THOMSON also guarantees 100 erase/write cycles and data retention exceeding 20 years.

## GAL16V8S Block Diagram

# GAL16V8S PAL® Architecture Emulation

| 16L8 | 16R8  | 16RP6 | 16L2 | 14L4 | 12L6 | 10L8 |

|------|-------|-------|------|------|------|------|

| 16H8 | 16RP8 | 16R4  | 16H2 | 14H4 | 12H6 | 10H8 |

| 16P8 | 16R6  | 16RP4 | 16P2 | 14P4 | 12P6 | 10P8 |

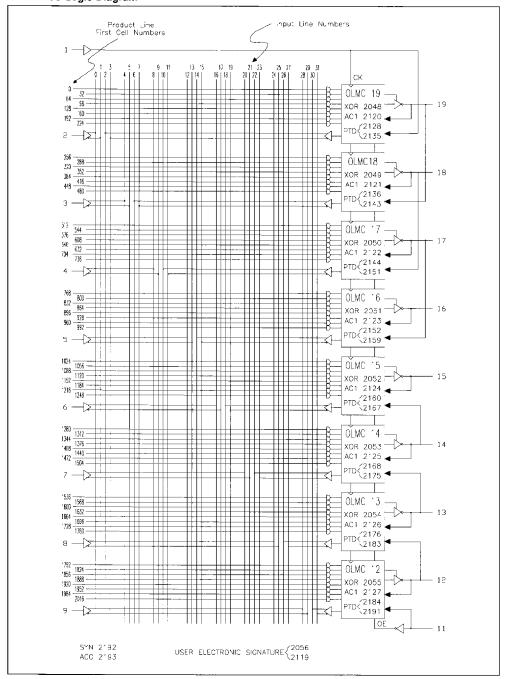

## GAL16V8S Logic Diagram

## **Absolute Maximum Ratings**

| Symbol | Parameter                                        | Value                      | Unit |

|--------|--------------------------------------------------|----------------------------|------|

| Vcc    | Supply Voltage                                   | -0.5 to +7                 | V    |

| Vı     | Input Voltage Applied                            | -2.5 to V <sub>CC</sub> +1 | ٧    |

| VB     | Off-State Output (Bidirectional) Voltage Applied | -2.5 to V <sub>CC+1</sub>  | ٧    |

| Tstg   | Storage Temperature                              | -65 to +125                | °C   |

| TJ     | Junction Temperature (Operating)                 | -40 to +125                | °C   |

| TL     | Lead Temperature (Soldering)                     | 260 (for 10s max.)         | °C   |

Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress only ratings and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied.

## **ESD Immunity**

Test Method: Human Body Model (HBM)

ESD Tolerance ≥ 2000V (See MIL-STD 883c).

Test Method: Charge Device Model (CDM)

ESD Tolerance ≥ 500V

Test Instrument: KeyTek ZapMaster

CDM is an additional test only for GAL®s not yet adopted as a company standard test.

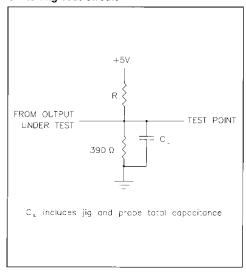

## **Switching Test Conditions**

| Input Pulse Levels                | GND to 3.0V |

|-----------------------------------|-------------|

| Input Rise and Fall Times         | 3ns 10%-90% |

| Input Timing Reference<br>Levels  | 1.5V        |

| Output Timing Reference<br>Levels | 1.5V        |

| Output Load                       | See figure  |

3-state levels are measured 0.5V from steady-state active level.

#### **Test Conditions**

| # | <b>R</b> [Ω]                      | C <sub>L</sub> [pF] |

|---|-----------------------------------|---------------------|

| 1 | 200                               | 50                  |

| 2 | Active High: ∞<br>Active Low: 200 | 50                  |

| 3 | Active High: ∞<br>Active Low: 200 | 5                   |

## **Switching Test Circuit**

# Capacitance (T<sub>A</sub>=25°C, f=1.0MHz, V<sub>CC</sub>=5V)

| Symbol | Parameter                     | Test Conditions    | Maximum <sup>+</sup> | Units |

|--------|-------------------------------|--------------------|----------------------|-------|

| Cı     | Input Capacitance             | V <sub>I=2</sub> V | 8                    | рF    |

| Св     | Bidirectional Pin Capacitance | V <sub>B</sub> =2V | 10                   | pF    |

<sup>&</sup>quot; Guarantied but not 100% tested.

## **DC Operating Conditions**

| Symbol | Parameter                 | Commercial<br>Temperature Range |                   | Indus<br>Temperatu    | Units             |    |

|--------|---------------------------|---------------------------------|-------------------|-----------------------|-------------------|----|

| •      | ,                         | Min.                            | Max.              | Min.                  | Max.              | ]  |

| Vcc    | Supply Voltage            | 4.75                            | 5.25              | 4.5                   | 5.5               | V  |

| TA     | Ambient Temperature       | 0                               | 70                | -40                   | 85                | °C |

| VIL    | Input Low Voltage         | VSS**-0.5                       | 0.8               | V <sub>SS</sub> *-0.5 | 0.8               | V  |

| ViH    | Input High Voltage        | 2.0                             | V <sub>CC+1</sub> | 2.0                   | V <sub>CC+1</sub> | V  |

| lOL.   | Low Level Output Current  |                                 | 24                | -                     | 24                | mA |

| Юн     | High Level Output Current | -3.2                            |                   | -3.2                  |                   | mA |

<sup>\*</sup> Vss is the voltage applied to the GND pin.

# **Electrical Characteristics Over Operating Conditions (Commercial Temperature Range)**

| Symbol   | Parameter                         | Test Conditions                                                                                    | Min. | Max. | Units |

|----------|-----------------------------------|----------------------------------------------------------------------------------------------------|------|------|-------|

| liH, liL | Input Leakage Current             | GND≤VI≤V CC <sub>Max</sub>                                                                         | _    | ±10  | μА    |

| IBH, IBL | Bidirectional Pin Leakage Current | GND≤VI≤V CC Max                                                                                    | _    | ±10  | μА    |

| loc      | Operating Power Supply Current    | f=15MHz<br>V <sub>CC</sub> = V <sub>CC Max</sub><br>V <sub>IL</sub> =0.5V<br>V <sub>IH</sub> =3.0V | _    | 27   | mA    |

| los*     | Output Short Circuit Current      | V <sub>CC</sub> =5.0V, V <sub>B</sub> =0.5V                                                        | -150 | -30  | mA    |

| VoL      | Output Low Voltage                |                                                                                                    | -    | 0.5  | V     |

| VoH      | Output High Voltage               | _                                                                                                  | 2.4  | _    | ٧     |

## **Electrical Characteristics Over Operating Conditions (Industrial Temperature Range)**

| Symbol   | Parameter                         | Test Conditions                                                         | Min. | Max. | Units |  |

|----------|-----------------------------------|-------------------------------------------------------------------------|------|------|-------|--|

| lih, lil | Input Leakage Current             | GND≤VI≤V CC <sub>Max</sub>                                              | _    | ±10  | μА    |  |

| IBH, IBL | Bidirectional Pin Leakage Current | GND≤VI≤V CC Max                                                         |      | ±10  | μA    |  |

| loc      | Operating Power Supply Current    | ating Power Supply Current  f=15MHz  VCC = V CC Max  VIL=0.5V  VIH=3.0V |      | 36   | mA    |  |

| los*     | Output Short Circuit Current      | V <sub>CC</sub> =5.0V, V <sub>B</sub> =0.5V                             | -150 | -30  | mA    |  |

| Vol      | Output Low Voltage                |                                                                         | _    | 0.5  | ٧     |  |

| Voн      | Output High Voltage               | _                                                                       | 2.4  | _    | V     |  |

<sup>\*</sup>One output at a time for a maximum duration of one second.

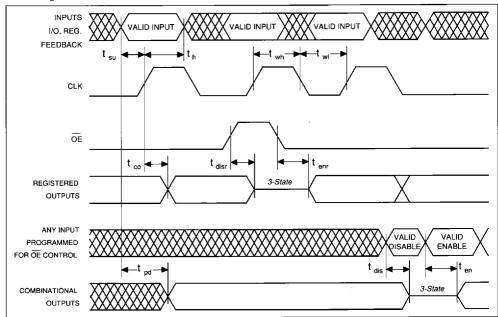

# **Switching Characteristics Over Operating Conditions**

| Symbol | Parameter                             | From  | То                | Max. | Units | Test Cond.* |

|--------|---------------------------------------|-------|-------------------|------|-------|-------------|

| tpd    | Combinational Propagation Delay       | Input | Output            | 20   | ns    | 1           |

| tco    | Clock to Output Delay                 | Clock | Registered Output | 15   | ns    | 1           |

| ten    | Product Term Output Enable to Output  | Input | Output            | 20   | ns    | 2           |

| tenr   | Output Register Enable to Output      | ŌĒ    | Registered Output | 18   | ns    | 2           |

| tdis   | Product Term Output Disable to Output | Input | Output            | 20   | ns    | 3           |

| tdisr  | Output Register Disable to Output     | ŌE    | Registered Output | 18   | ns    | 3           |

**AC Operating Conditions**

| Symbol              | Parameter                                        | Min. | Max. | Units | Test<br>Cond.* |

|---------------------|--------------------------------------------------|------|------|-------|----------------|

| tsu                 | Input or Feedback Setup Time (Before Clock Rise) | -    | 15   | ns    | . –            |

| th                  | Input or Feedback Hold Time (After Clock Rise)   |      | 0    | ns    | -              |

| twh                 | Minimum Clock Width High                         | _    | 12   | ns    | _              |

| twi                 | Minimum Clock Width Low                          | _    | 12   | ns    | _              |

| fclk <sup>♦</sup>   | Clock Frequency Without Feedback                 | 41.6 | _    | MHz   | 1              |

| f <sub>clkf</sub> + | Clock Frequency With Feedback                    | 33.3 | _    | MHz   | 1              |

<sup>\*</sup> Refer to "Switching Test Conditions".

## **Switching Waveforms**

$f_{clk} = \frac{1}{t_{wh} + t_{wl}} + f_{clkf} = \frac{1}{t_{su} + t_{co}}$

#### **FUNCTIONAL DESCRIPTION**

GAL16V8S has a programmable AND array whose output terms feed a fixed (non programmable) OR array, as bipolar PAL®. The 2 × 8 input lines enter the AND array as true or complemented form. 64 product terms are available allowing standard Sum of Products Logic implementation. Each product term is obtained by appropriate connections between the input lines and the product term line. The connections can be made by programming the E<sup>2</sup>PROM memory cell at each intersection of the AND matrix (2048 memory cells). The 64 product terms are divided into eight groups of 8 terms each. One product term for each group can be used to provide Output Enable control for combinational output, the others are connected with an OR gate into the corresponding OLMC (Output Logic Macrocell). The output buffer is in 3-state when the corresponding output enable signal is low.

#### OUTPUT LOGIC MACROCELL (OLMC)

The following discussion pertains to configuring the output logic macrocells. It should be noted that

actual implementation is accomplished by development software/hardware and is completely transparent to the user.

The outputs of the AND array are fed into an OLMC, where each output can be individually set to active high or active low, with either combinational (asynchronous) or registered (synchronous) configurations. A common output enable is connected to all registered outputs; product terms can be used to provide individual output enable control for combinational outputs. All outputs have always programmable polarity.

The output logic macrocell provides the designer with maximum output flexibility in matching signal requirements, thus providing more functions than existing 20 pin PAL® devices.

Three different configuration modes of the OLMCs are possible: registered, complex and simple. The output of an OLMC in registered mode can be either registered or combinational. Different modes cannot be mixed: i.e. all OLMCs of a device have to be configured in simple, complex or registered mode.

## GAL16V8S Output Logic Macrocell Pin 12 and 19

## GAL16V8S Output Logic Macrocell Pin 13 to 18

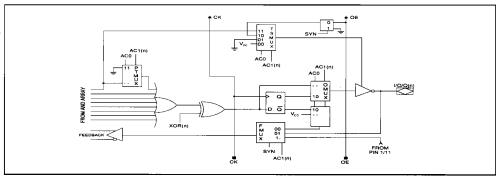

#### REGISTERED MODE

In registered mode macrocells are configured as registered outputs or combinational inputs/outputs. Any macrocell can be configured as registered output or combinational input/output. Up to 8 registered outputs or up to 8 inputs/outputs are possible in this mode.

All registered macrocells share common clock and output enable control. Registered outputs have 8 data product terms per output, while combinational inputs/outputs have only 7 data product terms per output: in the latter case the eighth product term serves as individual output enable control for each macrocell.

## Registered Output with Programmable Polarity

## Combinational Input/Output with Programmable OE and Polarity

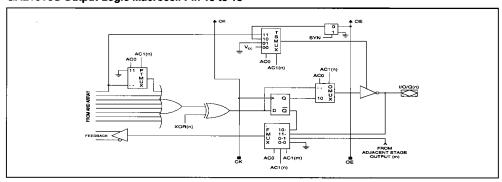

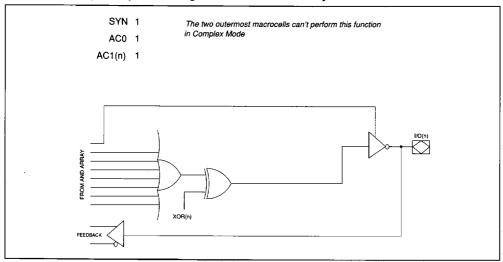

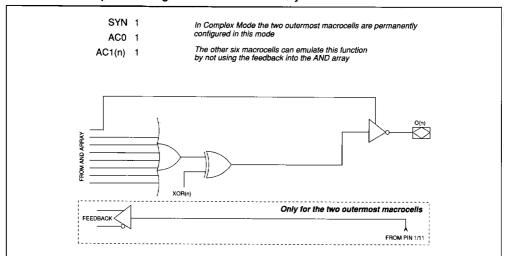

#### **COMPLEX MODE**

In complex mode macrocells are configured as combinational inputs/outputs or outputs only. The two outermost macrocells (12 and 19) do not have input capability: so only up to 6 inputs/outputs are possible in this mode. Applications requiring 8 inputs/outputs must be implemented in registered mode.

All macrocells have 7 data product terms per output; the eighth product term is used as individual output enable control for each macrocell. The clock and output enable pins (pins 1 and 11 respectively) are always available as inputs.

## Combinational Input/Output with Programmable OE and Polarity

## Combinational Output with Programmable OE and Polarity

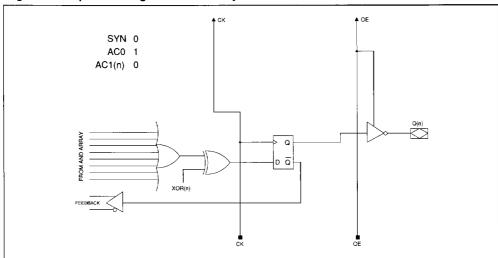

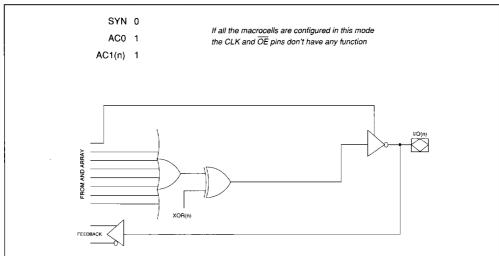

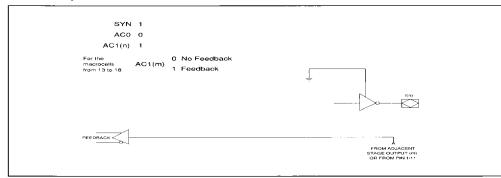

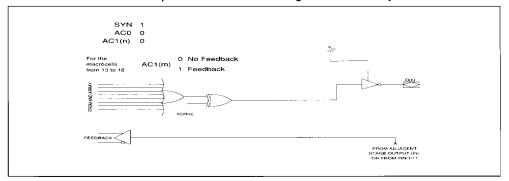

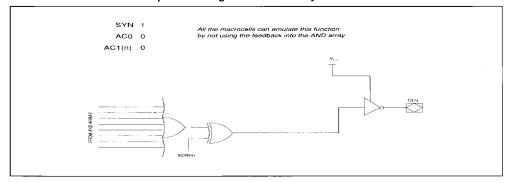

#### SIMPLE MODE

In simple mode macrocells are configured as dedicated inputs or as dedicated, always active, combinational outputs. The two central macrocells (15 and 16) cannot be used in the input configuration.

All macrocells have 8 data product terms per output. The clock and output enable pins (pins 1 and 11 respectively) are always available as inputs.

## **Dedicated Input Mode**

## Dedicated Combinational Output with Feedback and Programmable Polarity

## **Dedicated Combinational Output with Programmable Polarity**

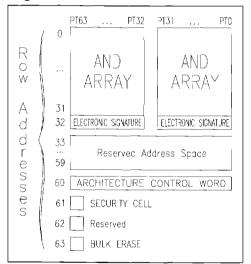

#### **ROW ADDRESS MAP DESCRIPTION**

There are a total of 36 unique row addresses available to the user when programming the GAL16V8S device. Row addresses 0-31 each contain 64 bits of input term data. This is the AND array where the custom logic pattern is programmed. Row 32 is the Electronic Signature Word. It has 64 bits available for any user defined purpose. Row 33-59 are reserved by the manufacturer and are not available to users.

Row 60 contains the architecture and output polarity information. The 82 bits within this word are programmed to configure the device for a specific application. Row 61 contains a one bit security cell that when programmed prevents further pattern verification of the array. Row 63 is the rcw that is addressed to perform a bulk erase of the device, resetting it back to a virgin state. Each of these functions is described in the following sections.

## GAL16V8S Row Addresses Map Block Diagram

## ELECTRONIC SIGNATURE WORD DESCRIPTION

An electronic signature word is provided with every GAL16V8S device. It resides at row address 32 and contains 64 bits of reprogrammable memory that can contain user-defined data. Some uses include user ID codes, revision numbers, or inventory control. This signature data is always available to the user independent of the state of the security cell.

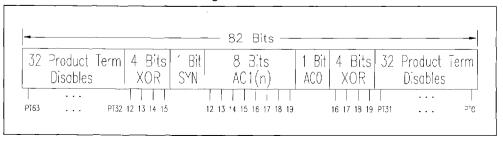

## ARCHITECTURE CONTROL WORD

All the various output configurations of the GAL16V8S devices are controlled by programming cells within the 82 bit Architecture Control Word that resides at row 60. The location of specific bits within the Architecture Control Word is shown in the control word diagram in figure below. The function of the SYN, AC0 and AC1(n) bits have been explained in the OUTPUT LOGIC MACROCELL description. The eight polarity bits determine each output's polarity individually. The numbers below the XOR(n) and AC1(n) bits in the architecture control word diagram shows the output device pin number that the polarity bits control.

#### SECURITY CELL

Row address 61 contains the Security Cell (one bit). The Security Cell is provided on all GAL16V8S devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, the circuitry enabling array access is disabled, preventing further verification of the array (rows 0-31). The cell can be erased only in conjunction with the array during a bulk erase cycle, so the original configuration can never be examined once this cell is programmed. Signature data is always available to the user.

#### **BULK ERASE MODE**

By addressing row 63 during a programming cycle, a clear function performs a bulk erase of the array and the Architecture Control Word. In addition, the Electronic Signature Word and the Security Cell are erased. This mode resets a previously configured device back to its virgin state.

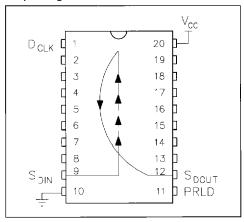

#### **OUTPUT REGISTER PRELOAD**

When testing state machine designs, all possible states and state transitions must be verified in the

## **GAL16V8S Architecture Control Word Diagram**

design, not just those required in the normal machine operations. This is because in system operation, certain events occur that may throw the logic into an illegal state (power-up, line voltage glitches, brown-outs, etc.). To test a design for proper management of these conditions, a way must be provided to break the feedback paths, and force any desired (e.g. illegal) state into a register. Then the machine can be sequenced and the outputs tested for the correct next state condition. The GAL16V8S device includes circuitry that allows each registered output to be synchronously set either high or low. Thus, any present state condition can be forced for test sequencing. If necessary, approved GAL programmers capable of executing test vectors can perform output register preload automatically.

The figure on the right shows the pin functions necessary to preload the register. This test mode is entered by raising PRLD to VIES (register preload input voltage, typically 15V), which enables the serial data in (SDIN) buffer and the serial data out (SDOUT) buffer. Data is then serially shifted into the registers on each rising edge of the clock, DCLK. Only the macrocells with registered output configurations are loaded. If only 3 outputs have registers, then only 3 bits need be shifted in. The registers are loaded from the bottom up as shown in the figure on the right.

#### LATCH-UP PROTECTION

GAL<sup>®</sup> devices are designed with an on board charge pump to negatively bias the substrate. The negative bias is of sufficient magnitude to prevent input undershoots from causing the circuitry to latch. Additionally, outputs are designed with n-channel pullups instead of the traditional p-channel pullups to eliminate any possibility of SCR induced latching.

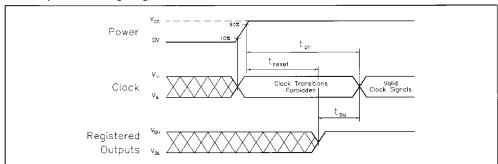

#### POWER-UP RESET

Circuitry within the GAL16V8S provides a reset signal to all registers during power-up. All internal registers will have their Q outputs set low after a specified time ( $t_{reset}$ =10 $\mu$ s). As a result, the state on the registered output pins (if they are enabled

#### **Output Register Preload Pinout**

through  $\overline{OE}$ ) will always be high on power-up, regardless of the programmed polarity of the output pins. This features can greatly simplify state machine design by providing a known state on power-up.

The timing diagram for power-up is shown below. Because of the asynchronous nature of system power-up, the V<sub>CC</sub> rise must be monotonic to guarantee a valid power-up reset of the GAL16V8S. The registers will reset within a maximum of  $t_{reset}$  time: before this time any clock transition from low to high is forbidden to avoid undesired commutations. As in normal system operation, avoid clocking the device until all input and feedback path setup times have been met (i.e. avoid clocking before the  $t_{pr}$ = $t_{reset}$ + $t_{su}$  time interval).

#### **DEVICES PROGRAMMING**

SGS-THOMSON strongly recommends the use of qualified programming hardware. Programming on unapproved equipment will invalidate all guarantees.

## Power-Up Reset Timing Diagram

12/15

#### TYPICAL CHARACTERISTICS

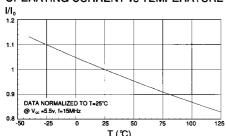

## **OPERATING CURRENT vs TEMPERATURE**

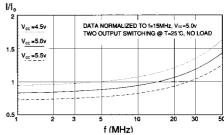

# OPERATING CURRENT vs FREQUENCY

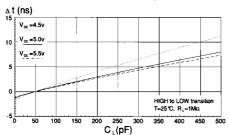

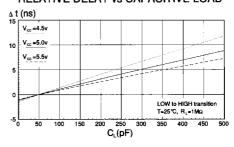

## RELATIVE DELAY vs CAPACITIVE LOAD

## RELATIVE DELAY vs CAPACITIVE LOAD

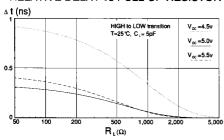

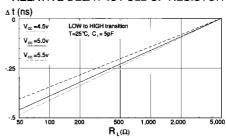

#### RELATIVE DELAY vs PULL-UP RESISTOR

#### RELATIVE DELAY vs PULL-UP RESISTOR

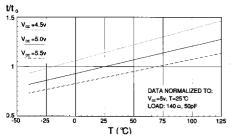

## NORMALIZED DELAY vs TEMPERATURE

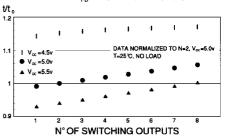

## NORMALIZED t po vs SWITCHING OUTPUTS

## PACKAGE MECHANICAL DATA

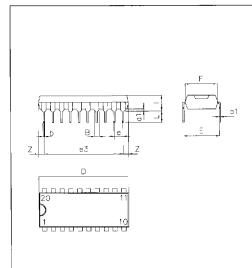

## PDIP 20 Pins

| Dim  |       | mm    |      | inches |       |       |  |

|------|-------|-------|------|--------|-------|-------|--|

| Dim. | Min   | Тур   | Max  | Min    | Тур   | Max   |  |

| a1   | 0.254 |       |      | 0.010  |       |       |  |

| В    | 1.39  |       | 1.65 | 0.054  |       | 0.064 |  |

| b    |       | 0.45  |      |        | 0.017 |       |  |

| b1   |       | 0.25  | -    |        | 0.009 |       |  |

| D    |       |       | 25.4 |        |       | 1.000 |  |

| E    |       | 8.50  |      |        | 0.334 |       |  |

| е    |       | 2.54  |      |        | 0.100 |       |  |

| e3   |       | 22.86 |      |        | 0.900 |       |  |

| F    |       |       | 7.10 |        |       | 0.279 |  |

| ł    |       |       | 3.93 |        |       | 0.154 |  |

| L    |       | 3.30  |      |        | 0.129 |       |  |

| Z    |       | 1.27  | 1.34 |        | 0.050 | 0.052 |  |

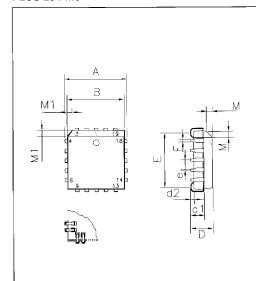

## **PLCC 20 Pins**

| Dim. | mm   |      |       | inches |       |       |

|------|------|------|-------|--------|-------|-------|

|      | Min  | Тур  | Max   | Min    | Тур   | Max   |

| Α    | 9.78 |      | 10.03 | 0.385  |       | 0.395 |

| В    | 8.89 |      | 9.04  | 0.350  |       | 0.356 |

| D    | 4.20 |      | 4.57  | 0.165  |       | 0.180 |

| d1   |      | 2.54 |       |        | 0.100 |       |

| d2   |      | 0.56 |       |        | 0.022 |       |

| Е    | 7.37 |      | 8.38  | 0.290  |       | 0.330 |

| е    |      | 1.27 |       |        | 0.050 |       |

| F    |      | 0.38 |       |        | 0.015 |       |

| М    |      | 1.27 |       |        | 0.050 |       |

| М1   |      | 1.14 |       |        | 0.045 |       |

Seating Plane: 0.101 mm/0.004 inches

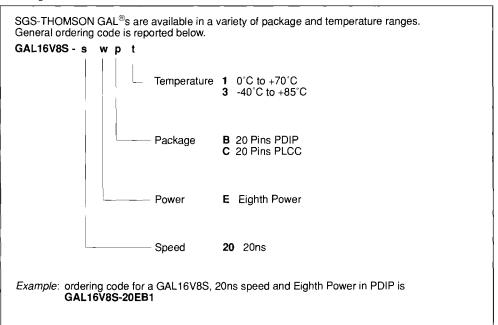

## Ordering Informations\*

<sup>\*</sup> Please contact local Product Marketing for latest update on package / temperature range availability.